# SED CD Drivers Technical Manual

No part of this material may be reproduced or duplicated in any from or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notics. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no repersentation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export licenes from the Ministry of International Trade and Industry or other approval from another government agency.

HD44103, HITACHI Ltd.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

©Seiko Epson Corporation 1998 All rights reserved.

#### **CONTENTS**

#### **SED1700 Series Selection Guide**

- 1. SED1741D1B

- 2. SED1742

- 3. SED1743

- 4. SED1744

- 5. SED1748D0B

- 6. SED1752

- 7. SED1753

- 8. SED1758

- 9. SED17A2

- 10. SED1765

- 11. SED1766

- 12. SED1770

# **SED1700 Series Selection Guide**

#### **SED1700 Series Selection Guide**

#### ■LCD drivers for large-sized displays

High-speed drivers for large-sized dot-matrix displays that complement SEIKO EPSON's dedicated LCD controllers.

SED1700 series

#### Segment drivers

| Part number             | Supply voltage range (V) | LCD voltage range (V) | Duty   | Outputs | Outputs Data bus Package |                                            | Application           |

|-------------------------|--------------------------|-----------------------|--------|---------|--------------------------|--------------------------------------------|-----------------------|

| SED1722D0A              |                          |                       |        |         | 4-bit                    | Al pad chip                                |                       |

| SED1722F0A              | 4.5–5.5                  |                       |        | 80      | parallel                 | QFP5-100pin                                | Used with the SED1733 |

| SED1724D0A              | 4.5-5.5                  |                       |        | 80      | 8-bit                    | Al pad chip                                | Used with the SED1733 |

| SED1724F0A              | 1                        | 14Å 40                |        |         | parallel                 | QFP5-100pin                                |                       |

| SED1742D1B              |                          | 14A 40                |        |         | 4-bit                    | Au bump chip                               |                       |

| SED1742T0A              | ]                        |                       |        |         |                          | TCP (Outer lead pitch 0.18mm)              |                       |

| SED1744D1B              |                          |                       |        |         |                          | Au bump chip                               |                       |

| SED1744T0A              |                          |                       |        | 1/100   |                          | TCP (Outer lead pitch 0.18mm)              | _                     |

| SED1748D0B              |                          |                       | 1/100  |         |                          | Au bump chip                               |                       |

| SED1748T0A              |                          |                       | -1/500 | 100     |                          | TCP (Outer lead pitch 0.092mm)             |                       |

| SED1758D0B              | 2.7–5.5                  |                       |        |         |                          | Au bump chip                               | Used with the SED1743 |

| SED1758T0A              | 2.1-3.3                  |                       |        |         | 8-bit                    | Slim TCP (Outer lead pitch 0.092 mm)       |                       |

| SED1758ToB              | 1                        | 14–42                 |        |         | parallel                 | Flex TCP (Outer lead pitch 0.092 mm)       |                       |

| SED1758Tog              |                          | 14-42                 |        |         |                          | Ultra slim TCP (Outer lead pitch 0.080 mm) |                       |

| SED1752T0A              | 1                        |                       |        |         |                          | Slim TCP (Outer lead pitch 0.070 mm)       |                       |

| SED1752ToB              | 1                        |                       |        | 040     |                          | Ultra slim TCP (Outer lead pitch 0.070 mm) |                       |

| SED17A0Toa <sup>*</sup> | ]                        |                       |        | 240     |                          | Ultra slim TCP (Outer lead pitch 0.070 mm) |                       |

| SED1756D0A              | 1                        |                       |        |         |                          | Al pad chip (For COG)                      | Used with the SED1755 |

#### Common Drivers

\* : Under development

| Part number            | Supply voltage range (V) | LCD voltage range (V) | Duty            | Outputs | Package                       | Application           |

|------------------------|--------------------------|-----------------------|-----------------|---------|-------------------------------|-----------------------|

| SED1733D0A             | 4.5-5.5                  |                       | 1/100           | 100     | Al pad chip                   |                       |

| SED1733F0A             | 4.5-5.5                  | 14–40                 | -1/400          | 100     | QFP5-128pin                   |                       |

| SED1743D1B             |                          | 14-40                 |                 | 160     | Au bump chip                  |                       |

| SED1743T0A             |                          |                       |                 |         | TCP (Outer lead pitch 0.18mm) |                       |

| SED1741D1B             |                          |                       | 4/400           | 100     | Au bump chip                  |                       |

| SED1741T <sub>1B</sub> | 2.7–5.5                  |                       | 1/100<br>-1/500 | 100     | TCP                           |                       |

| SED1753D0B             |                          | 14–42                 | 17000           | 120     | Au bump chip                  |                       |

| SED1753T0A             |                          |                       | 120             |         | TCP                           |                       |

| SED1755D0A             |                          |                       |                 | 240     | Al pad chip (For COG)         | Used with the SED1756 |

<sup>\*:</sup> Under development

## ■LCD drivers for grayscale displays

#### MIM LCD Drivers SED1760 series

Controlling the lighting time, they avail gray-scale displays in 16 or 64 levels on the LCD panel. The applicable type of panel differs depending on the speed, withstanding voltage and driving method.

| Part number | Supply voltage range (V) | LCD voltage range (V) | Duty        | Segment | Common | Data bus           | Package                        | Application           |

|-------------|--------------------------|-----------------------|-------------|---------|--------|--------------------|--------------------------------|-----------------------|

| SED1765D0A  |                          |                       |             |         |        |                    | Al pad chip                    | For MIM-type displays |

| SED1765D0B  |                          |                       |             |         |        |                    | Au bump chip                   | PWM technology        |

| SED1765T0A  | 1 45.55                  | 44.40                 | 1/100–1/500 | 160     | -      | 4-bit parallel x 2 | TCP (Outer lead pitch: 0.18mm) | 16-level gray         |

| SED1766D0A  | 4.5–5.5                  | 14–40                 |             |         |        |                    | Al pad chip                    | For STN-type displays |

| SED1766D0B  |                          |                       |             |         |        |                    | Au bump chip                   | PWM technology        |

| SED1766T0A  |                          |                       |             |         |        |                    | TCP (Outer lead pitch: 0.18mm) | 16-level gray         |

#### • TFT LCD Drivers

SED1770 series

| Part number        | Supply voltage range (V) | LCD voltage range (V) | Duty | Segment outputs | Data inputs | Package        | Application          |  |

|--------------------|--------------------------|-----------------------|------|-----------------|-------------|----------------|----------------------|--|

| SED1770D0A         | 4555                     | 5–17                  | -    | 160             | 3           | Au bump chip   | For MIM- or TFT-type |  |

| SED1771D0A 4.5–5.5 |                          | 5-17                  | -    | 162             | (R,G,B)     | Au builip chip | displays             |  |

# 9. SED17A2 LCD Segment Driver

#### **Contents**

| 1.  | OVERVIEW                    | . 9-1 |

|-----|-----------------------------|-------|

| 2.  | FEATURES                    | . 9-1 |

| 3.  | BLOCK DIAGRAM               | . 9-1 |

| 4.  | BLOCK FUNCTIONS             | . 9-2 |

| 5.  | PIN DESCRIPTION             | . 9-4 |

| 6.  | ABSOLUTE MAXIMUM RATING     | . 9-5 |

| 7.  | ELECTRIC CHARACTERISTICS    | . 9-6 |

| 8.  | LCD DRIVE POWER SUPPLY      | 9-10  |

| 9.  | SAMPLE CIRCUIT              | 9-11  |

| 10. | TCP                         | 9-13  |

| 11. | DIMENSIONAL OUTLINE DRAWING | 9-14  |

#### 1. OVERVIEW

SED17A2T is a 240-output segment (column) driver suited for large capacity, color STN dot matrix liquid crystal panels. It is used paired with the SED1753.

It is designed for high resolution LCD display, employs high speed enable chain technique for achieving low-power and equips with long type chip layout suited for smaller LCD panels. SED17A2T's low voltage, high speed logic operation capability offers it a wide range of applications.

#### 2. FEATURES

- LCD drive outputs: 240

- Lower operating voltage: 2.7V minimum

- Applicable to high duty drive: 1/500 (for reference)

Wide LCD drive voltage range:

+8V to +42V (VCC = 3 to 5.5V)

High speed and low-power data transfer supported by the 8 bit bus, enable chain approach

Shift clock frequency ...30.0MHz (5V±10%) ...20.0MHz (3.0V) ...18.0MHz (2.7V)

- · Slimmer chip shape

- Non-bias display off function

- Pin selectable output shift direction

- LCD power bias is offset adjustable according to VDDH or GND level

- Logic operation power: 2.7V to 5.5V

- Package: TCP... SED17A2T\*\*

- This IC is not designed for radiation and light protection

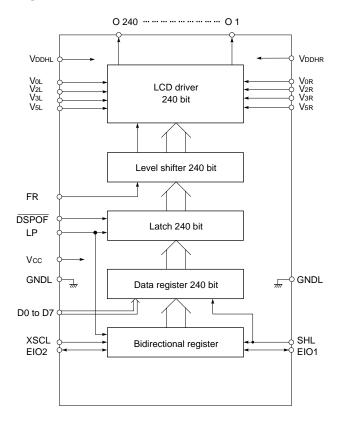

#### 3. BLOCK DIAGRAM

#### 4. BLOCK FUNCTIONS

#### **Enable register**

Enable register is a bidirectional register which allows direction select by the SHL input. The shift register output is used for storing the data bus signal to the data register.

As long as the enable signal is disabled, the internal clock signal and data bus are fixed to low-level to introduce the power save mode to the system.

When multiple segment drivers are used, EIO terminals on respective drivers are cascade connected and EIO terminal on the first driver is connected to GND (see the connection example). The enable control circuit automatically detects the end of acquisition of 240 bit of data and transfers the enable signal automatically. Therefore, control signal from the control LSI is no more needed.

#### Data register

It is a register for converting the data bus signal to and from parallel and serial using the enable shift register output. Therefore, relations between serial display data and segment output is determined independent of number of shift clocks entered.

#### Latch

Acquires the data register contents at the LP falling edge trigger, then sends it to the level shifter.

#### Level shifter

A level interface circuit for converting voltage level of a signal from logic system level to LCD drive level.

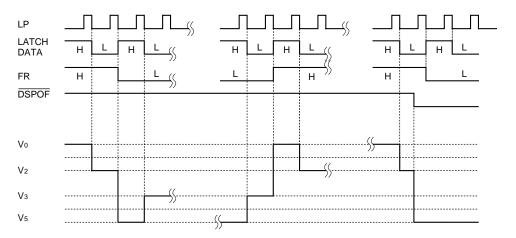

#### LCD driver

Outputs the LCD drive voltage.

The following table shows relations between data bus signal, frame signal FR and segment output voltage.

| DSPOF | Data bus signal | FR | Driver output voltage |

|-------|-----------------|----|-----------------------|

|       | Н               | Н  | Vo                    |

|       | П               | L  | V5                    |

| Н     |                 | Н  | V2                    |

|       | L               | L  | Vз                    |

| L     | _               | _  | V5                    |

9–2 EPSON

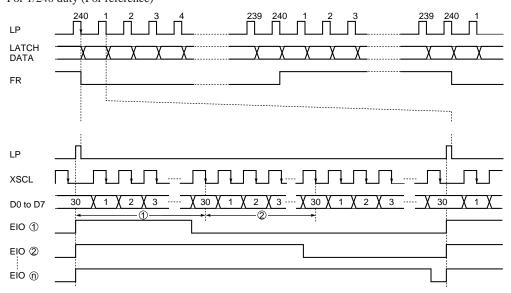

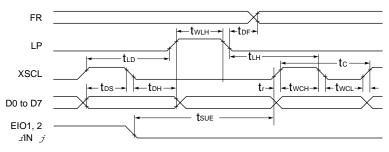

#### **Timing Diagram**

Timing Diagram For 1/240 duty (For reference)

① and ① represent the driver cascade number.

\* In high speed data transfer, a longer XSCL cycle must be selected in the LP pulse insertion timing for satisfying the LP-XSCL (tlh) requirement.

EPSON 9-3

#### 5. PIN DESCRIPTION

| Pin name                                                    | I/O          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                    |                     |                          | escr            | iptio   | n      |      |                     |        | No. of pins |

|-------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-----------------|---------|--------|------|---------------------|--------|-------------|

| O1 to O240                                                  | 0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | drive s                                                                                                                                                                                                                                                            |                     |                          | lumn            | ) outp  | out. T | he o | utput cl            | nanges | 240         |

| D0 to D3-7                                                  | I            | Displa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Display data input                                                                                                                                                                                                                                                 |                     |                          |                 |         |        |      |                     |        | 8           |

| XSCL                                                        | 1            | Displa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ay dat                                                                                                                                                                                                                                                             | a shif              | t clocl                  | κ inpι          | ıt (fal | ling e | edge | trigger             | )      | 1           |

| LP                                                          | I            | Displa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ay dat                                                                                                                                                                                                                                                             | a latc              | h puls                   | e inp           | ut (fa  | alling | edge | trigge              | r)     | 1           |

| EIO1<br>EIO2                                                | I/O          | It is s<br>input<br>auton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Enable input or output.  It is set to either input or output depending on the SHL  Input level. The output is reset as the LP is entered and  Input level as 160 bit of data has been acquired.                                                                    |                     |                          |                 |         |        |      |                     | 2      |             |

| SHL                                                         | I            | The fine segmine in the segment in t | Shift direction select and EIO pin I/O control signal input. The following shows the relation between data and segment output when data is entered to (D0 through D7) pins in the order of F0 through F7 being followed by L0 through and L7.  F (First), L (last) |                     |                          |                 |         |        |      |                     | 1      |             |

|                                                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                    |                     | 0 (0                     | Outpu           | t)      |        | `    | E                   | IO 1   |             |

|                                                             |              | SHL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | O240                                                                                                                                                                                                                                                               | O239                | O238                     |                 | O3      | O2     | 01   | EIO1                | EIO2   |             |

|                                                             |              | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F7                                                                                                                                                                                                                                                                 | F6                  | F5                       | •••             | L2      | L1     | L0   | Output              | Input  |             |

|                                                             |              | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L0                                                                                                                                                                                                                                                                 | L1                  | L2                       | •••             | F5      | F6     | F7   | Input               | Output |             |

|                                                             |              | Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                    |                     |                          |                 |         |        |      | ent out<br>of shift |        |             |

| FR                                                          | I            | LCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | drive                                                                                                                                                                                                                                                              | outpu               | ıt fram                  | ne sig          | ınal ir | nput.  |      |                     |        | 1           |

| Vcc, GNDL<br>GNDR                                           | Power supply | Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | opera                                                                                                                                                                                                                                                              | ation p             | oower                    | G               | ND :    | ۷ V0   | /cc: | +3.3V,              | +5V    | 3           |

| VDDHL, V0L<br>V2L, V3L,V5L,<br>VDDHR, V0R,<br>V2R, V3R, V5R | Power supply | LCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LCD drive circuit power $ \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                       |                     |                          |                 |         |        |      |                     | 10     |             |

| DSPOF                                                       | I            | At lov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | v-leve<br>s func                                                                                                                                                                                                                                                   | l, it fo<br>tion is | d inpurces the not a SED | he ou<br>availa | ble v   |        |      | I.<br>SED17         | A2T is | 1           |

9–4 EPSON

#### 6. ABSOLUTE MAXIMUM RATING

| Items                 | Codes          | Ratings               | Units |

|-----------------------|----------------|-----------------------|-------|

| Supply voltage (1)    | Vcc            | -0.3 to +7.0          | V     |

| Supply voltage (2)    | VDDH           | -0.3 to +45.0         | V     |

| Supply voltage (3)    | V0, V2, V3, V5 | GND -0.3 to VDDH +0.3 | V     |

| Input voltage         | Tı             | GND -0.3 to Vcc +0.3  | V     |

| Output voltage        | Vo             | GND -0.3 to Vcc +0.3  | V     |

| EIO output current    | loı            | 20                    | mA    |

| Operating temperature | Topr           | -30 to +85            | °C    |

| Storage temperature   | Tstg           | -55 to +100           | °C    |

Note 1: GND = 0V is assumed for all voltages.

Note 2: Storage temperature assumes that TCP has been mounted.

Note 3: V<sub>0</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>5</sub> voltage must always satisfy V<sub>DDH</sub>  $\geq$  V<sub>0</sub>  $\geq$  V<sub>2</sub>  $\geq$  V<sub>3</sub>  $\geq$  V<sub>5</sub>  $\geq$  GND.

Note 4: Do not allow the logic operation power goes to floating state or VCC goes to 2.6V or less while LCD drive circuit power is applied. Otherwise, LSI can be permanently damaged. Special care is needed for the system power on or off sequences.

#### 7. ELECTRIC CHARACTERISTICS

#### **DC Characteristics**

Except where otherwise specified,  $GND = V_5 = 0V$ ,  $VCC = +5.0V \pm 10\%$  and Ta = -30 to  $85^{\circ}C$  are assumed.

| Items                               | Codes          | Con                                                                                                                      | nditions                                                           | Min.      | Тур. | Max.   | Units | Applicable pins                      |

|-------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------|------|--------|-------|--------------------------------------|

| Supply voltage (1)                  | Vcc            |                                                                                                                          |                                                                    | 2.7       | _    | 5.5    | V     | Vcc                                  |

| Recommended operating voltage       | V <sub>0</sub> |                                                                                                                          |                                                                    | 14.0      | _    | 40.0   | V     | Vol, VDDHL                           |

| Operatable voltage                  | Vo             | Function                                                                                                                 |                                                                    | 8.0       | _    | 42.0   | V     | Vor, VDDHL                           |

| Supply voltage (2)                  | V2             | Recomm                                                                                                                   | nended value                                                       | 7/9Vo     | _    | Vo     | V     | V <sub>2</sub> L, V <sub>2</sub> R   |

| Supply voltage (3)                  | Vз             | Recomm                                                                                                                   | nended value                                                       | GND       | _    | 2/9Vo  | V     | V3L,V3R                              |

| High level input voltage            | ViH            | Vcc = 2                                                                                                                  | 2.7 to 5.5V                                                        | 0.8Vcc    | _    | _      | V     | EIO1, EIO2, FR<br>D0 to D7, XSCL     |

| Low level input voltage             | VIL            |                                                                                                                          |                                                                    | _         | _    | 0.2Vcc | V     | SHL, LP, DSPOF                       |

| High level output voltage           | Vон            | Vcc =                                                                                                                    | Iон = - 0.6mA                                                      | Vcc - 0.4 | _    | _      | V     | EIO1, EIO2                           |

| Low level output voltage            | Vol            | 2.7 to 5.5V                                                                                                              | Iон = 0.6mA                                                        | _         |      | 0.4    | V     |                                      |

| Input leak current                  | lu             | GND ≤                                                                                                                    | GND ≤ VIN ≤ Vcc                                                    |           | _    | 2.0    | μА    | D0 to D7, LP, FR<br>XSCL, SHL, DSPOF |

| I/O leak current                    | Ili/O          | GND ≤                                                                                                                    | ≤ Vin ≤ Vcc                                                        | _         | _    | 5.0    | μΑ    | EIO1, EIO2                           |

| Rest current                        | IGND           |                                                                                                                          | to 42.0V<br>c, VIL = GND                                           | _         | _    | 25     | μА    | GND                                  |

| Output resistance                   | Rseg           | ΔVon<br>= 0.5V                                                                                                           | Vo<br>= +36.0V, 1/24                                               | _         | 0.80 | 1.1    | kΩ    | O0 to                                |

|                                     |                | Recommende condition                                                                                                     | d Vo<br>= +26.0V, 1/20                                             | _         | 0.85 | 1.2    | _     | O240                                 |

| Output resistance in-chip deviation | ΔRseg          | $\Delta Von = 0.5$<br>Vo = +36.0                                                                                         |                                                                    | _         | _    | 95     | Ω     | O1 to<br>O240                        |

| Mean operating current (1)          | Icc            | VIL = GND,<br>f <sub>LP</sub> = 33.6Kl<br>Input data:                                                                    | V, VIH = VCC<br>fxscL = 5.38MHz<br>Hz, fFR = 70Hz<br>blay, no load | _         | 0.75 | 1.7    | mA    | Vcc                                  |

|                                     |                |                                                                                                                          | V<br>litions are the<br>hen Vcc = 5V                               |           | 0.3  | 0.9    |       |                                      |

| Mean operating current (2)          | lo             | $V_0=+30.0V$ $V_{CC}=+5.0V,\ V_3=+4.0V$ $V_2=+26.0V,\ V_5=0.0V$ Other conditions are the same as shown in the Icc column |                                                                    | _         | 0.25 | 1.4    | mA    | Vo                                   |

| Input terminal capacity             | Сі             | Freq. 1MHz Ta = 25°C                                                                                                     |                                                                    | _         | _    | 8      | pF    | D0 to D7, LP, FR<br>XSCL, SHL, DSPOF |

| I/O terminal capacity               | Cı/o           | Independer                                                                                                               | nt chips                                                           | _         | _    | 15     | pF    | EIO1, EIO2                           |

9-6 EPSON

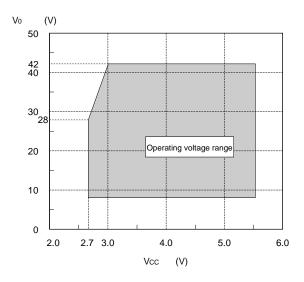

#### Operating Voltage Range Vcc-Vo

V0 voltage must be selected within the VCC-V0 operating voltage range as shown below.

#### AC Characteristics

#### **Input Timing Characteristics**

$(VCC = +5.0V\pm10\%, Ta = -30 \text{ to } 85^{\circ}C)$

| Items                       | Codes                    | Conditions          | Min. | Max. | Units |

|-----------------------------|--------------------------|---------------------|------|------|-------|

| XSCL cycle                  | <b>t</b> c               | *2                  | 33   | _    | ns    |

| XSCL high-level pulse width | <b>t</b> wcH             |                     | 9    | _    | ns    |

| XSCL low-level pulse width  | twcL                     | 20% and 80% of Vcc  | 9    | _    | ns    |

| Data setup time             | <b>t</b> DS              | are assumed for all | 5    | _    | ns    |

| Data hold time              | <b>t</b> dh              | timing.             | 5    | _    | ns    |

| XSCL→LP rise time           | <b>t</b> ld              |                     | -0   | _    | ns    |

| LP→XSCLE fall time          | <b>t</b> LH              |                     | 25   | _    | ns    |

| LP high-level pulse width   | twlh                     | *1                  | 15   | _    | ns    |

| Allowable FR delay time     | <b>t</b> DF              |                     | -300 | +300 | ns    |

| EIO setup time              | <b>t</b> sue             |                     | 5    | _    | ns    |

| Input signal change time    | <b>t</b> r1, <b>t</b> f1 | *3                  | _    | 50   | ns    |

| DSPOF signal change time    | <b>t</b> r2, <b>t</b> f2 |                     | _    | 100  | ns    |

$(VCC = +2.7V \text{ to } 4.5V, Ta = -30 \text{ to } 85^{\circ}C)$

| Items                       | Codes                    | Conditions          | Min. | Max. | Units |

|-----------------------------|--------------------------|---------------------|------|------|-------|

| XSCL cycle                  | tc                       | Vcc = 3.0 to 4.5V   | 50   | _    | ns    |

|                             |                          | *2                  | 55   | _    | ns    |

| XSCL high-level pulse width | <b>t</b> wcH             |                     | 15   | _    | ns    |

| XSCL low-level pulse width  | twcL                     | 20% and 80% of Vcc  | 15   | _    | ns    |

| Data setup time             | tos                      | are assumed for all | 10   | _    | ns    |

| Data hold time              | tон                      | timing.             | 10   | _    | ns    |

| XSCL→LP rise time           | <b>t</b> LD              |                     | -0   | _    | ns    |

| LP→XSCLE fall time          | tьн                      |                     | 30   | _    | ns    |

| LP high-level pulse width   | twlh                     | *1                  | 25   | _    | ns    |

| Allowable FR delay time     | <b>t</b> DF              |                     | -300 | +300 | ns    |

| EIO setup time              | tsue                     |                     | 10   | _    | ns    |

| Input signal change time    | <b>t</b> r1, <b>t</b> f1 | *3                  | _    | 50   | ns    |

| DSPOF signal change time    | <b>t</b> r2, <b>t</b> f2 |                     | _    | 100  | ns    |

<sup>\*1:</sup> tWLH regulates high-level period of LP and low-level period of XSCL if LP is entered while XSCL is at low-level.

9–8 EPSON

<sup>\*2:</sup> High speed shift clock (XSCL) operation is regulated by the condition tr+tf ≤ (tc-twcL-twcH).

<sup>\*3:</sup> When high speed data transfer is done with continuous shift clock, maximum of the LP signal fr+tf is (tc+twch-tld-twl+tlh).

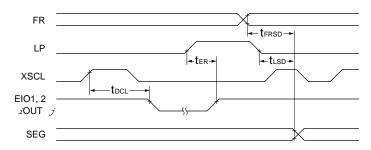

#### **Output Timing Characteristics**

$(Vcc = +5.0V\pm10\%, Vo = +14.0 \text{ to } 42.0V)$

| Items                    | Codes         | Conditions       | Min. | Max. | Units |

|--------------------------|---------------|------------------|------|------|-------|

| EIO reset time           | <b>t</b> er   | CL (EIO) = 15pF  | _    | 50   | ns    |

| EIO output delay time    | <b>t</b> DCL  | OL (LIO) = 13pi  | _    | 25   | ns    |

| LP→SEG output delay time | <b>t</b> LSD  | CL (On) = 100pF  | _    | 200  | ns    |

| FR→SEG output delay time | <b>t</b> FRSD | GE (OII) = 100pF | _    | 400  | ns    |

(VCC = +2.7V to 4.5V, V0 = +14.0 to 28.0V)

| Items                    | Codes         | Conditions      | Min. | Max. | Units |

|--------------------------|---------------|-----------------|------|------|-------|

| EIO reset time           | <b>t</b> er   | CL (EIO) = 15pF | _    | 80   | ns    |

| EIO output delay time    | <b>t</b> DCL  |                 | _    | 50   | ns    |

| LP→SEG output delay time | <b>t</b> LSD  | CL (On) = 100pF | _    | 400  | ns    |

| FR→SEG output delay time | <b>t</b> FRSD |                 | _    | 800  | ns    |

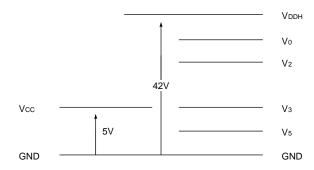

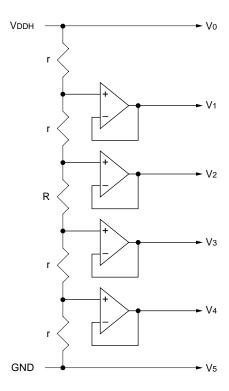

# 8. LCD DRIVE POWER SUPPLY Setting up different voltage levels

When setting up respective voltage levels for LCD drive, the best way would be to resistively divide the potential between Vo-GND by means of voltage follower using an operation amplifier. In consideration of the case of using an operation amplifier, the LCD driving minimum potential V5 and GND are separated and independent terminals are used.

However, since efficacy of the LCD driving output driver deteriorates when the potential of V5 goes up beyond the GND potential, the potential difference between V5-GND must always be kept at 0V to 2.5V.

When a resistance exists in series in the V0 (GND) power supply line, I0 at signal changes causes voltage drop at V0 (GND) of the LSI supply terminals disabling it to maintain the relations with the LCD potentials of (VDDH =  $V0 \ge V2 \ge V3 \ge V5 \ge GND$ ). This could result in permanent damage of the LSI.

When a protective resister is employed, the voltage must be stabilized using an appropriate capacitance.

### Precautions for turning power on or off

Since the LCD drive voltage of these LSIs are high, if a voltage of 30V or above is applied to the LCD drive circuit when the logic operation power is floating, the VCC is lowered to 2.6V or less or LCD drive signals are output before applied voltage to the LCD drive circuit is stabilized, excess current flows through possibly damaging the LSI.

It is therefore suggested to maintain the potential of the LCD drive to V5 level until the LCD drive circuit power is stabilized. Use the display off function (DSPOF) for this purpose.

Maintain the following sequences when turning power on or off.

When turning power on: Turn on the logic operation power → turn on the LCD drive power or turn them on simultaneously.

When turning power off: Turn off the LCD drive power  $\rightarrow$  turn off the logic operation power or turn them off simultaneously.

As a protection against excess current, insert a quick melting fuse in series in the LCD drive power line.

When using a protective resistor, an optimum resistance value must be selected considering the capacitance of the liquid crystal cells.

9–10 EPSON

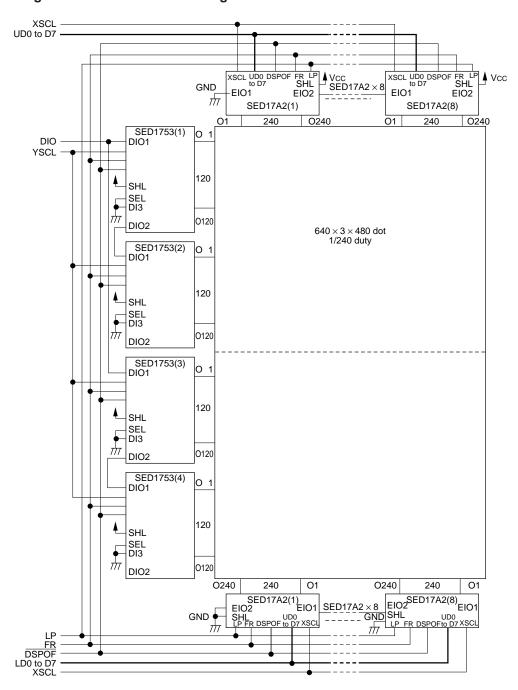

#### 9. SAMPLE CIRCUIT

#### Large Screen LCD Structural Diagram

#### A Sample LCD Power Supply

- Smoothing capacitance must be added to the LCD drive power (V0-V5) at an appropriate position on the LCD module.

- V0, V1, V4 and V5 supply power to the SED1753 and V0, V2, V3 and V5 are used supplying power to the SED17A2T.

- Supplies logic operation voltage to respective ICs.

- Bias capacitors must be installed to appropriate positions between GND-VCC and GND-VDDH for stabilizing voltage and, thus, to provide protection against noise.

The high tension resistant power (GNDR, GNDL) line might as well be separated from that for the logic operation power (GND) line.

9–12 EPSON

#### 10.TCP

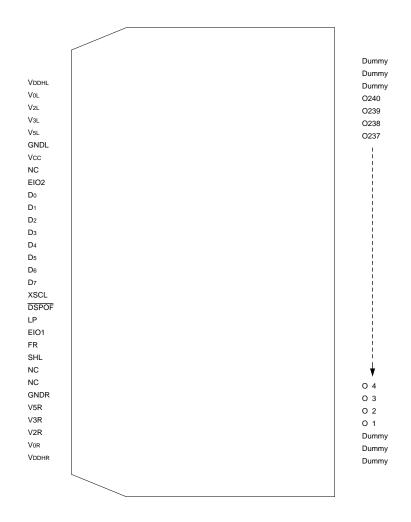

#### Sample SED17A2T\*\* TCP Pin Layout

Note: It is not intended to regulate contour of TCP.

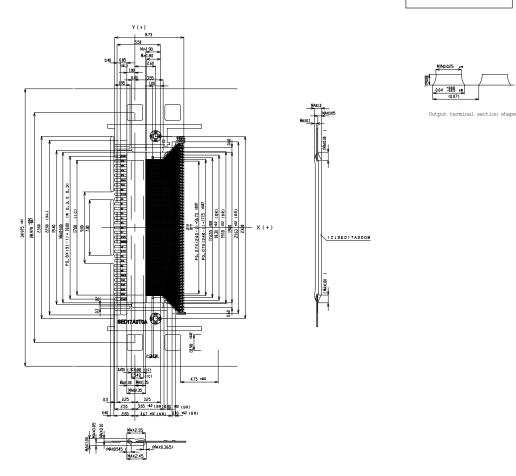

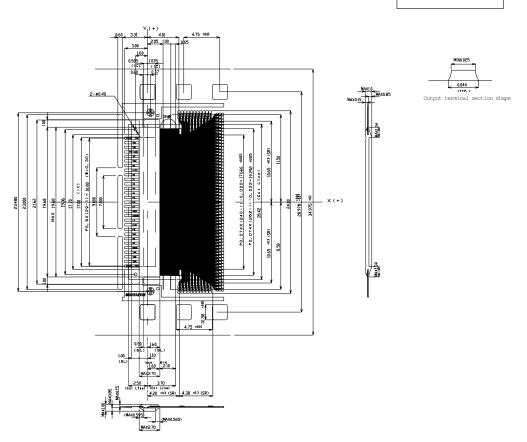

# 11. DIMENSIONAL OUTLINE DRAWING SED17A2T0A

#### For reference

Unit: mm

9–14 EPSON

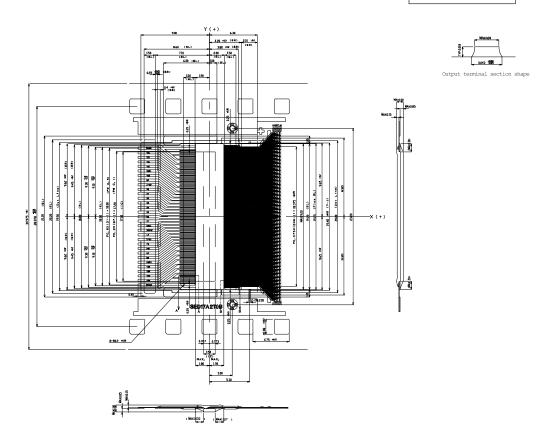

#### SED17A2T0B

#### For reference

Unit: mm

#### SED17A2T0E

#### For reference

Unit: mm

9–16 EPSON